## **Classical CMOS Scaling**

# **Is it Really Dead?**

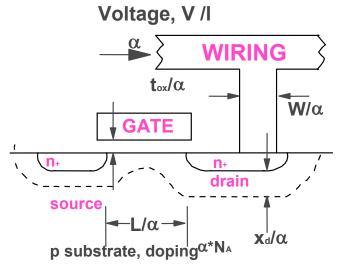

#### **SCALING:**

Voltage:  $V/\alpha$ Oxide:  $t_{ox}/\alpha$ Wire width:  $W/\alpha$ Gate width:  $L/\alpha$ Diffusion:  $x_d/\alpha$ Substrate:  $\alpha * N_\Delta$

### **RESULTS:**

Higher Density:  $\sim a^2$ Higher Speed:  $\sim a$ Power/ckt:  $\sim 1/a^2$

Power Density:~Constant

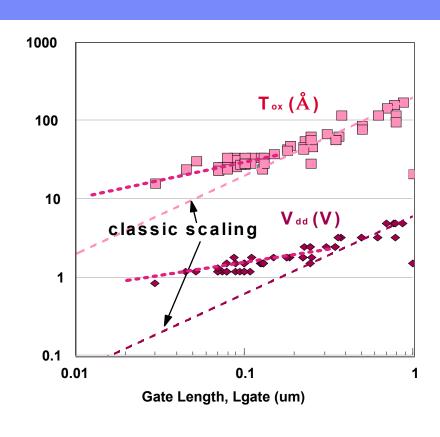

### Why deviate from "ideal" scaling

- unacceptable gate leakage/reliability

- additional performance at higher voltage What is consequence of this deviation?

- a dramatic rise in power density